## SYSC3601 Microprocessor Systems

# Unit 9: The Motorola 68000 μP

- 1. Overview of the 68000  $\mu P$

- 2. Programming model, assembly, addressing modes, stack

- 3. 68000 Hardware interfacing, bus arbitration

- 4. Read/Write cycles

- 5. Memory organization

- 6. Memory interfacing

- 7. I/O interfacing

- 8. Exception processing, hardware interrupts

#### Reading: Antonakos, chapters 1,2,3,4,7,8,9,12

- 6800  $\mu$ P introduced in 1974, 8-bit.

- 68000  $\mu$ P introduced in Sept 1979.

- NMOS (N-channel MOS technology)

- 68K transistors?

- 64 Pin DIP (8086 is 40)  $\rightarrow$  No multiplexing.

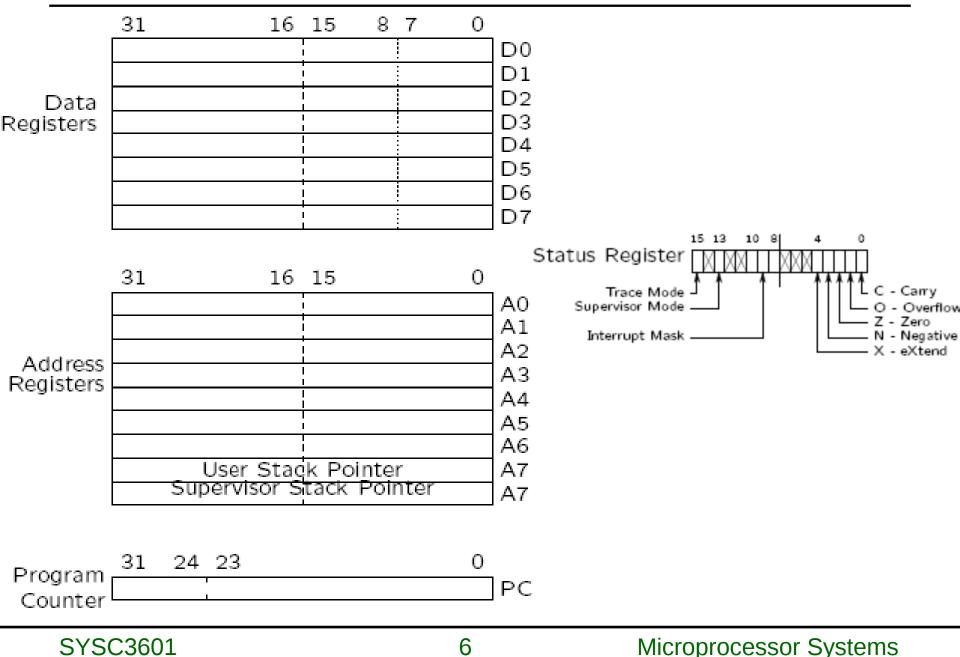

- Internal architecture is 32 bits (ALU is 16 bits wide).

- 23 bit (physical) address bus  $A_1 A_{23}$ . No  $A_0$ .

- (24 bit effective address bus with LDS/UDS...)

- 16 bit data bus.

- Operands:

- Bytes

- Words (16-bits)

- Long words (32-bits)

- 68008 8 bit data bus, 20 bit address bus.

- 68010 1982. Added virtual memory support.

- 68020 1984. Fully 32 bit. 3 stage pipeline.

256 byte cache. More addressing modes!

- 68030 1987. Integrated MMU into chip.

- **68040** 1991. Harvard architecture with two 4KB caches. FP on chip. 6 stage pipeline.

- **68060** 1994. Superscalar version . 10-stage pipeline. 2 integer, 1 fp unit. 8k caches. 4-5W.

- **Coldfire** 1995. Embedded version. Stripped out funky addressing modes.

- Used in:

- Apple Macintosh (then PPC, now Intel!!).

- Atari 520ST and 1040ST (Defunct).

- Amiga (Defunct).

- Early Sun workstations (Now SPARC).

- NeXT (Defunct, purchased by Apple 1996, MAC OS X came from 'NeXTStep').

- 68000 architecture has user/supervisor modes.

- protects operating system.

- supports multitasking and multiprocessing.

#### Motorola 68000 µP – Programming Model

### Motorola 68000 $\mu$ P - Assembler

- format: INST SRC, DST

- Prexes:

- -% binary

- \$ Hexadecimal

- # Immediate.

- Attach size to instruction, e.g.:

- move.b byte

- move.w word

- move.l long word

- `()' refers to indirect addressing – (recall that Intel uses `[]').

Motorola 68000  $\mu$ P – Assembler Examples

- move.b #\$F5,d1

- Store immediate (#) hex (\$) byte (.b), \$F5 into destination d1. 8-bit transfer.

- move.w (a2),d1

- stores contents of memory addressed by a2 into data register d1. 16-bit transfer.

- add.l d4,d5

- Add 32-bit contents of register d4 to d5 and store the results in d5. Set flags.

#### Motorola 68000 $\mu$ P – Addressing Modes

| • | There are 14 different addressing modes (more with the 68020!) Mode Syntax |                                                                             |  |

|---|----------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|

|   | Data reg direct                                                            | d <sub>n</sub> , n = 07                                                     |  |

|   | Addr reg direct                                                            | a <sub>n</sub> , n = 07                                                     |  |

|   | Addr reg indirect                                                          | (a <sub>n</sub> )                                                           |  |

|   | with Postincrement                                                         | (a <sub>n</sub> )+                                                          |  |

|   | with Predecrement                                                          | -(a <sub>n</sub> )                                                          |  |

|   | with Displacement                                                          | d <sub>16</sub> (a <sub>n</sub> )                                           |  |

|   | with Index                                                                 | $d_8(a_n, X_m)$ ( $X_m$ is any $a_m$ or $d_m$ )                             |  |

|   | Relative with offset                                                       | d <sub>16</sub> (PC)                                                        |  |

|   | Relative with index and offset                                             | $d_{8}(PC, X_{n})$                                                          |  |

|   | Absolute short                                                             | < … > (16-bits sign-extended to 32)<br>(for 000000-007FFF or FF8000-FFFFFF) |  |

|   | Absolute long                                                              | < > (32-bits)                                                               |  |

|   | Immediate                                                                  | #< >                                                                        |  |

|   | Quick immediate                                                            | <pre>#&lt; &gt; (1 byte, sign-extend to 32)</pre>                           |  |

|   | Implied                                                                    | Register specified as part of mnemonic                                      |  |

| S | SYSC3601                                                                   | 9 Microprocessor Systems                                                    |  |

Motorola 68000  $\mu$ P – Addressing Mode Examples

- move.b #\$6f,d0

- Immediate

- move.w d3,d4

- data reg direct. Lower 16 bits of d3 are copied to low 16-bits of d4, upper d4 not changed

- movea.l a5,a2

- address reg direct. Size must be .w or .1; .w implies sign extension

- move.b (a0),d7

- address register indirect. Byte pointed at by a0 copied to d7

- move.w (a5)+,d2

- post-increment. Word pointed at by a5 copied to d2, a5 then incremented by two (.w)

- move.b -(a2),d4

- pre-decrement. a2 decremented by one, then byte pointed at by a2 copied to d4

Motorola 68000  $\mu$ P – Addressing Mode Examples

• move.w \$100(a0),d0

- addr reg indirect with displacement. Contents of memory at  $a0+100_{16}$  copied to d0

- move.b \$08(a0,d1.w),d0

- addr reg indir with index. Note: can specify size here! Uses  $b_{15}$ - $b_0$  of d1 only (addr=a0+d1.w+\$08)

- move.b \$9AE0,d1

- *absolute short*. Sign extend to get data from address \$FF9AE0.

- move.b \$2E0000,d4

- Absolute long

- moveq #\$2C,d3

- *Quick Immediate*. Byte only (data encoded within instruction word). Byte is sign-extended to 32 bits.

### Motorola 68000 $\mu$ P – Addressing Mode Examples

• Example: A sample assembler subroutine for the 68000: Total: Find the sum of 16-bytes stored in memory.

| total<br>loop | subq.b<br>bne<br>movea.l | #16,d1  | <pre>;load program counter<br/>;clear D0.<br/>;initialize counter<br/>;init pointer to data<br/>;add byte, increment address<br/>;decrement counter<br/>;test for zero, branch not equal.<br/>;load address to store result<br/>;store sum at sum<br/>;return from subroutine.</pre> |

|---------------|--------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sum<br>data   | dc.w<br>ds.b<br>end      | 0<br>16 | ;save room for result.<br>;save room for 16 data bytes.                                                                                                                                                                                                                              |

- Note:

- dc.w define a constant word, operand specifies the value to be written.

- ds.b define storage byte, operand specifies number of bytes, but not the contents

### Motorola 68000 $\mu$ P – Stack

- Address register a7 is used to point to the stack.

- There are no push or pop instructions

- (except for pea push effective address).

- A push is done with:

- 1. Decrement a7 by four,

- 2. Write 32 bits to stack

- Actually implemented as:

- 1. Decrement a7 by two.

- 2. Write low word of d3

- 3. Decrement a7 by two.

- 4. Write high word of d3

• A pop is done with

move.l (a7)+,d3

- Stack grows down (towards lower addresses)

- pea Push Effective Address.

pea \$40(a5)

- Effective address is sum of a5 and 40.

- Result is pushed.

- jsr, rts Subroutine calls

- Push/pop program counter and branch.

#### Motorola 68000 $\mu$ P – Instruction Set

#### **TABLE 2.1**68000 instruction set

| Data transfer group |                                        | Shift and rotate group     |                          |

|---------------------|----------------------------------------|----------------------------|--------------------------|

| EXG                 | Exchange registers                     | ASL                        | Arithmetic shift left    |

| LEA                 | Load effective address                 | ASB                        | Arithmetic shift right   |

| LINK                | Link and allocate                      | LSL                        | Logical shift left       |

| MOVE                | Move data                              | LSE                        | 9                        |

| MOVEA               | Move address                           |                            | Logical shift right      |

| MOVEM               | Move multiple registers                | ROL                        | Rotate left              |

| MOVEP               | Move peripheral data                   | ROR                        | Rotate right             |

| MOVEQ               | Move guick                             | ROXL                       | Rotate left with extend  |

| PEA                 | Push effective address                 | ROXR                       | Rotate right with extend |

| SWAP                | Swap register halves                   | Dit r                      | manipulation group       |

| UNLK                | Unlink                                 | Dit 1                      | nanipulation group       |

|                     | Arithmetic group                       | BCHG                       | Bit change               |

|                     | Antimetic group                        | BCLR                       | Bit clear                |

| ADD                 | Add binary                             | BSET                       | Bit set                  |

| ADDA                | Add address                            | BTST                       | Bit test                 |

| ADDI                | Add immediate                          | Binary coded decimal group |                          |

| ADDQ                | Add quick                              |                            |                          |

| CLR                 | Clear operand                          | ABCD                       | Add BCD                  |

| CMP                 | Compare                                | NBCD                       | Negate BCD               |

| CMPA                | Compare address                        | SBCD                       | Subtract BCD             |

| CMPI                | Compare immediate                      | Program control group      |                          |

| CMPM                | Compare memory                         |                            | gram control group       |

| DIVS                | Divide signed numbers                  | Bcc*                       | Conditional branch       |

| DIVU                | Divide unsigned numbers                | DBcc*                      | Decrement and branch     |

| EXT                 | Extend sign                            | Scc*                       | Conditional set          |

| MULS                | Multiply signed numbers                | BRA                        | Branch always            |

|                     |                                        |                            |                          |

| MULU                | Multiply unsigned numbers              | BSR                        | Branch to subroutine     |

| NEG                 | Negate                                 | JMP                        | Jump                     |

| NEGX                | Negate with extend                     | JSR                        | Jump to subroutine       |

| SUB                 | Subtract binary                        | RTR                        | Return and restore       |

| SUBA                | Subtract address                       | RTS                        | Return from subroutine   |

| SUBI                | Subtract immediate                     | System control group       |                          |

| SUBQ<br>SUBX        | Subtract quick<br>Subtract with extend |                            | AND immediate to SR      |

| TAS                 | Test and set                           | ANDI SR                    |                          |

|                     |                                        | EORI SR                    | EOR immediate to SR      |

| TST                 | Test                                   | MOVE SR                    | Move to/from SR          |

|                     | Logical group                          | MOVE USP                   | Move to/from USP         |

|                     |                                        | ORISR                      | OR immediate to SR       |

| AND                 | Logical AND                            | RESET                      | Reset processor          |

| ANDI                | AND immediate                          | RTE                        | Return from exception    |

| OR                  | Logical OR                             | STOP                       | Stop processor           |

| ORI                 | OR immediate                           | СНК                        | Check register           |

| EOR                 | Exclusive OR                           | ILLEGAL                    | Illegal instruction      |

| EORI                | Exclusive OR immediate                 | TRAP                       | Trap call                |

| NOT                 | Logical complement                     | TRAPV                      | Trap on overflow         |

|                     | Logical complement                     |                            | AND immediate to CCR     |

|                     |                                        | ANDI CCR                   |                          |

|                     |                                        | ORI CCR                    | OR immediate to CCR      |

|                     |                                        | EORI CCR                   | EOR immediate to CCR     |

|                     |                                        | MOVE CCR                   | Move to/from CCR         |

|                     |                                        | NOP                        | No operation             |

\*Note: cc stands for condition code

15

#### **Microprocessor Systems**

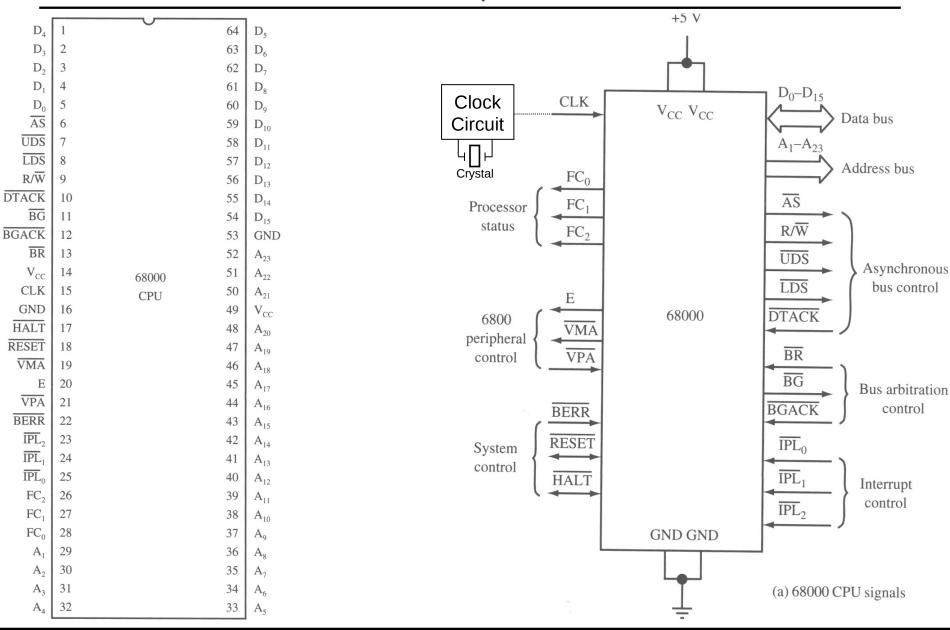

#### Motorola 68000 $\mu$ P – Hardware

• 16-bit  $\mu$ P - 16-bit data bus ( $D_{15}$ - $D_{0}$ ).

- Internal data paths are 32 bit

• 24-bit address bus.

- ( UDS, LDS,  $A_1 - A_{23}$ )

- No multiplexing of busses!

- Clock speeds of 4-12.5 MHz.

- 10/12/16/20 MHz for CMOS version (1/10th power consumption)

Note that we will use 'd7' for data register d7 and 'D7' for data bus line D7. Likewise for a7 vs. A7.

#### Motorola 68000 $\mu$ P – Hardware

#### Microprocessor Systems

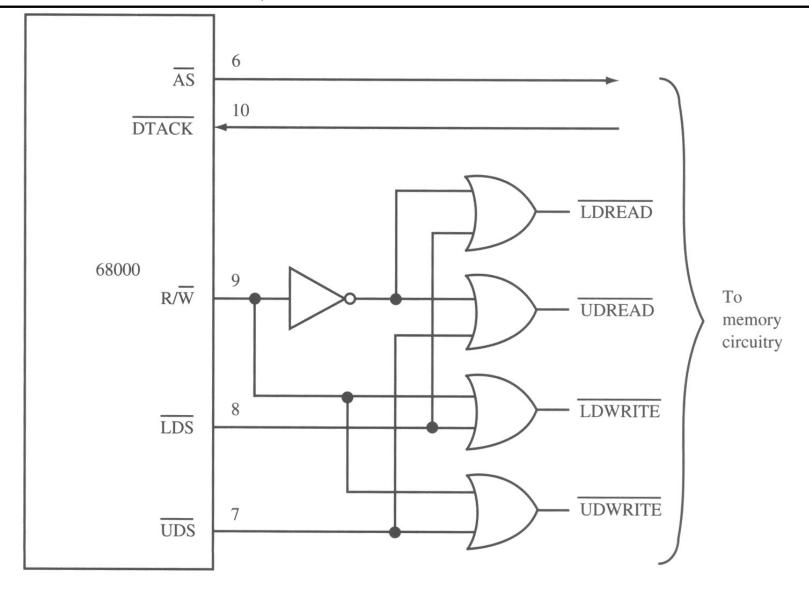

Motorola 68000  $\mu$ P – Asynchronous bus control

- AS Address strobe: valid address is on address bus.

- $R/\overline{W}$ : for read, 0 for write.

- $\overline{\text{UDS}}$ : Upper data strobe. Data on  $D_{15}$ - $D_8$  (like BHE).

- LDS: Lower data strobe. Data on  $D_7$ - $D_0$  (like BLE).

- DTACK: Data transfer acknowledge.

- Signal by external hardware that µP may complete the current bus cycle.

- During read,  $\mu P$  latches data when DTACK = 0.

- During write,  $\mu P$  puts data on bus and keeps it there until DTACK = 0.

#### Motorola 68000 $\mu$ P – Asynchronous bus control

**FIGURE 7.12** Decoding memory read/write signals

#### Motorola 68000 $\mu$ P – Hardware

- System control

- RESET: reset the  $\mu$ P. (in)

- HALT:  $\mu$ P puts the busses into high-impedance state

- (Equivalent to HOLD on 8086) (in/out).

- BERR: Bus error illegal memory location (in)

- YOU must generate this if DTACK or VPA never returns

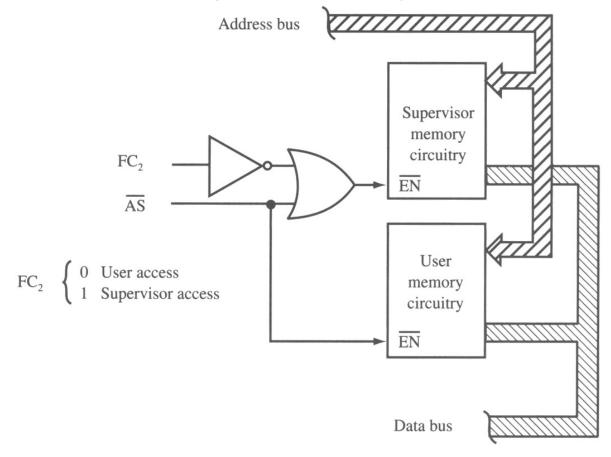

### Motorola 68000 $\mu$ P – Hardware

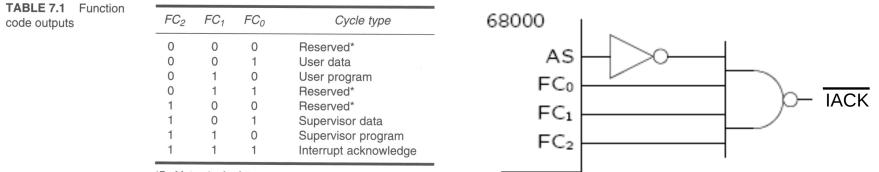

- $FC_0$ ,  $FC_1$ ,  $FC_2$ :

- Encoded processor states.

- only valid with AS = 0 (address strobe).

- $FC_{0}FC_{1}FC_{2} = 111$ : interrupt acknowledge.

\*By Motorola, for future use.

- $IPL_0$ ,  $IPL_1$ ,  $IPL_2$

- Encoded interrupt priority level.

- Seven interrupt levels.

- Level 7 (all zeros) is highest

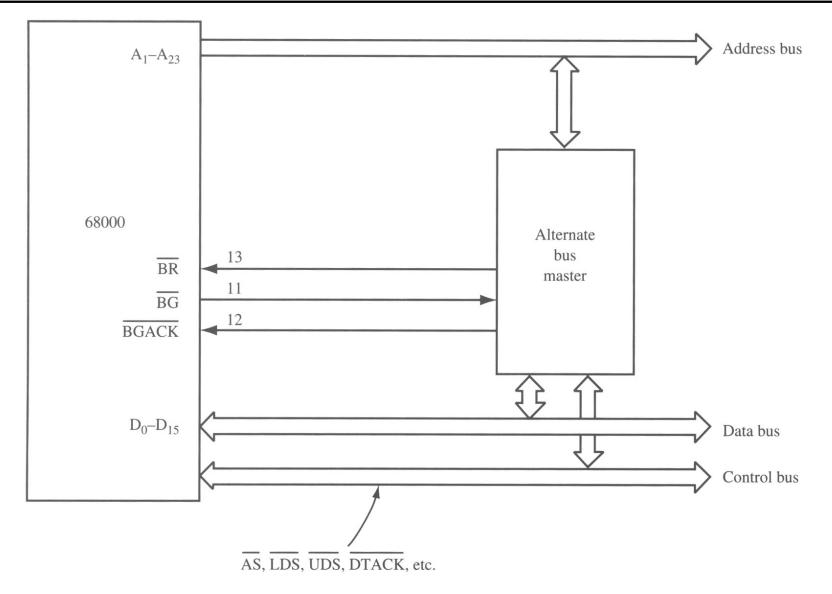

### Motorola 68000 $\mu$ P – Bus arbitration

- Bus arbitration control:

- BR: Bus request (in)

- $-\overline{BG}$ : Bus grant (out)

- BGACK: Bus grant acknowledgment (in)

- Used to place 68000 busses in high impedance state so that a peripheral can use the bus.

- Sequence:

- 1. External device sets  $\overline{BR} = 0$ .

- 2. 68000 sets  $\overline{BG} = 0$ .

- 3. External device waits for  $\overline{BG} = 0$ ,  $\overline{AS} = 1$ , DTACK = 1, BGACK = 1, then will set BGACK = 0 to take control of busses.

#### Motorola 68000 $\mu$ P – Bus arbitration

FIGURE 7.11 Bus arbitration logic block diagram

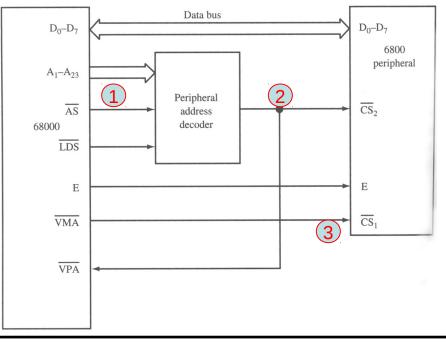

#### Motorola 68000 $\mu$ P – Hardware

- Interface to 6800 peripherals:

- E: Clock (out)

- VPA: Valid Peripheral address (in).

- Should be asserted by interface circuitry whenever a 6800 peripheral has been selected.

- VMA: Valid Memory address (out).

- Asserted by  $\mu P$  when internal clock is in synch with E-clock. Connected to second peripheral CS pin.

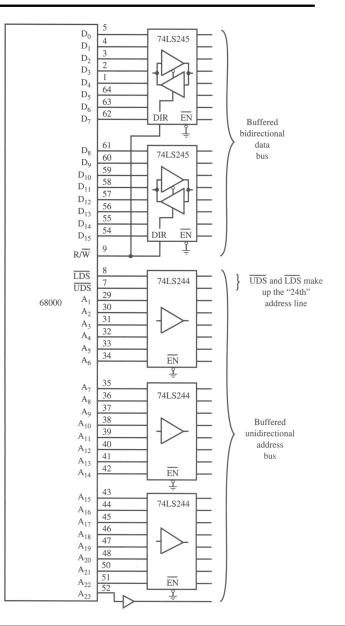

### Motorola 68000 $\mu$ P – Fully Buffered 68000

FIGURE 7.13 Buffering the address and data buses

**TABLE 7.3**Summaryof 68000 signals

| Signal                             | Input        | Output       | Tristate     |

|------------------------------------|--------------|--------------|--------------|

| CLK                                | 1            |              |              |

| FC <sub>0</sub> -FC <sub>2</sub>   |              | 1            | $\checkmark$ |

| E<br>VMA                           |              | 1            | /            |

| VPA                                | ./           | <i>√</i>     | $\checkmark$ |

| BERR                               | <i>✓</i>     |              |              |

| RESET                              | 1            | $\checkmark$ |              |

| HALT                               | $\checkmark$ | $\checkmark$ |              |

| IPL <sub>0</sub> -IPL <sub>2</sub> | $\checkmark$ |              |              |

| BR                                 | $\checkmark$ |              |              |

| BG                                 |              | 1            |              |

| BGACK<br>AS                        | $\checkmark$ | <i>,</i>     | ,            |

| AS<br>R/W                          |              | <i>s</i>     | <i>J</i>     |

| UDS                                |              | ./           | ✓<br>✓       |

| LDS                                |              | √<br>√       | 1            |

| DTACK                              | 1            |              | ·            |

| A <sub>1</sub> -A <sub>23</sub>    |              | $\checkmark$ | $\checkmark$ |

| D <sub>0</sub> -D <sub>15</sub>    | $\checkmark$ | 1            | $\checkmark$ |

25

#### Microprocessor Systems

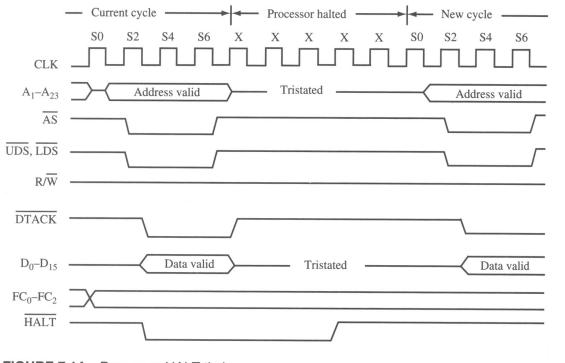

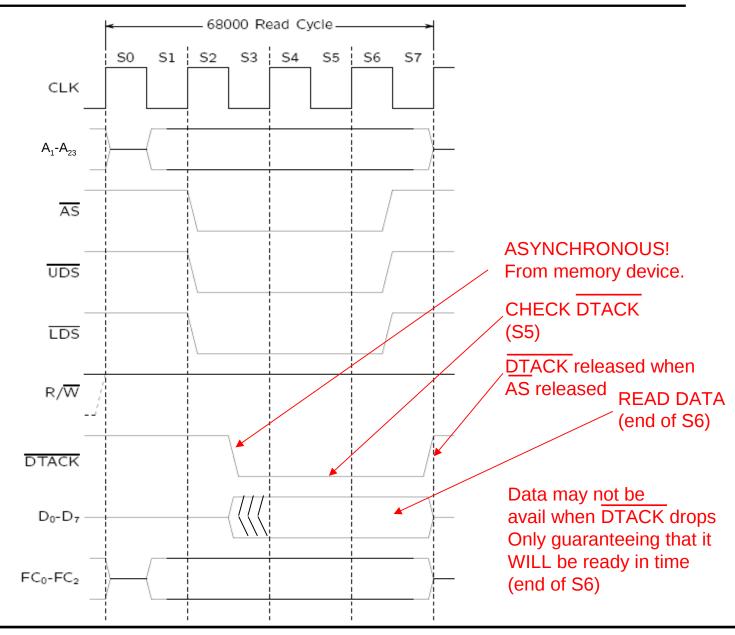

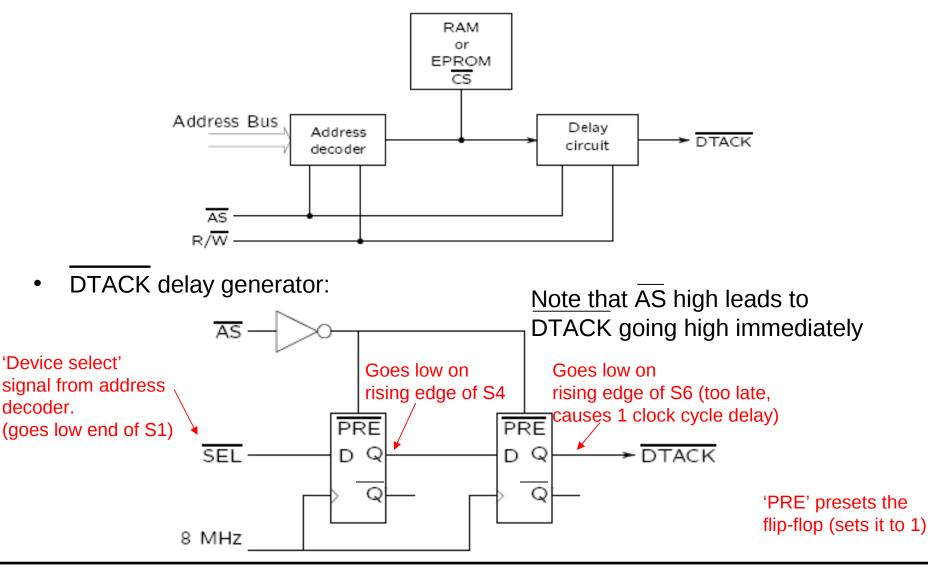

- The 68000 $\mu$ P uses  $\overline{AS}$ =0 to signal a memory access.

- When memory sees AS=0, and it is the correct address, it responds by pulling DTACK low which tells the μP to proceed with the data transfer.

- Bus cycles are divided into a minimum of eight states, S0 - S7. Each state is 1/2 a clock cycle.

### Motorola 68000 $\mu$ P – Read Cycle

- **SO**: Address bus is in high impedance state, R/W is set to 1 (read operation).

- **S1**: Valid address appears on address bus.

- **S2**: AS goes low (valid address), LDS and UDS are set to the desired state.

- **S3**,**S**<u>4</u>: Minimum time given to memory to signal with DTACK=0.

- **S5**:  $\mu P \log ks$  for DTACK=0.

- if DTACK=1, insert two wait states then test DTACK again.

- if  $\overline{\text{DTACK}}=0$ , continue with S6 and S7.

- **S6**: Nothing new happens.

- **S7**: Latch data into  $\mu P$ , set AS, UDS, and LDS to 1. Memory releases DTACK

#### Motorola 68000 $\mu$ P – Read Cycle

SYSC3601

28

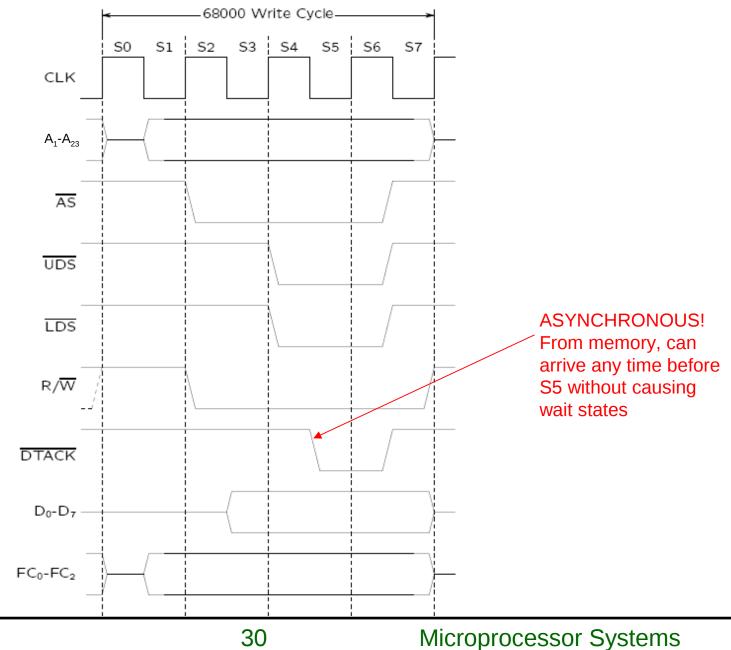

### Motorola 68000 $\mu$ P – Write Cycle

- **SO**: Address bus is in high impedance state.

- **S1**: Valid address appears on address bus.

- **S2**: AS goes low (valid address), R/W is set to 0 (write operation). (LDS and UDS are delayed to allow the bus transceivers to switch direction, and to allow the memory time to prepare.)

- **S3**: Valid data is placed on the bus by the  $\mu P$ .

- **S4**:  $\overline{\text{LDS}}$  and  $\overline{\text{UDS}}$  are set to the desired state.

- **S5**:  $\mu$ P looks for DTACK=0.

- if  $\overline{\text{DTACK}}=1$ , insert two wait states then test  $\overline{\text{DTACK}}$  again.

- if  $\overline{\text{DTACK}}$ =0, continue with S6 and S7.

- **S6**: Nothing new happens.

- **S7**: Set AS, UDS, and LDS to 1. Memory releases DTACK

#### Motorola 68000 µP – Write Cycle

SYSC3601

30

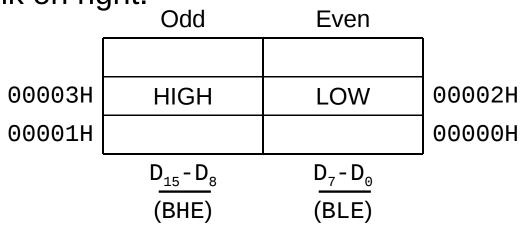

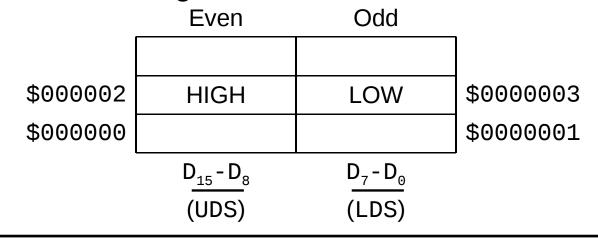

Motorola 68000  $\mu$ P – Memory Organization

- 68000 is byte-addressable.

- 16-bit words and 32-bit long words must begin at an even address, otherwise address error.

- 68000 is a big-endian processor:

- 16-bit words are stored with the lower-order byte (endian) in the higher-order (big) memory address.

- (Recall that the 8086 is little-endian)

- Consequences:

|                                 | Bank       |            |

|---------------------------------|------------|------------|

|                                 | 8086       | 68000      |

| D <sub>7</sub> -D <sub>0</sub>  | Even (BLE) | Odd (LDS)  |

| D <sub>15</sub> -D <sub>8</sub> | Odd (BHE)  | Even (UDS) |

Motorola 68000  $\mu$ P – Memory Organization

• 8086 memory is usually drawn with *odd* bank on left, and *even* bank on right.

68000 memory is usually drawn with even bank on left, and odd bank on right.

Motorola 68000  $\mu$ P – Memory Organization

• Ex 68000 memory segment:

|          | Even   | Odd   |          |

|----------|--------|-------|----------|

|          | (High) | (Low) |          |

| \$00100A | C3     | 8F    | \$00100B |

| \$001008 | 3F     | 6B    | \$001009 |

| \$001006 | 00     | 4A    | \$001007 |

| \$001004 | 23     | 08    | \$001005 |

- Byte@\$1004 = \$23 (high half)

- Byte@\$1005 = \$08 (low half)

- Word@\$1006 = \$004A (both halves)

- Word@\$1008 = \$3F6B (both halves)

- Word@\$1009 = Address Error

- Long word@\$1008 = \$3F6BC38F (both halves, twice)

- Long word@\$1005 = Address Error

33

- Almost identical to the 8086 except:

- 1. Switch even and odd banks

- 2. Must generate DTACK

- 3. Must use  $\overline{AS}$ , R/W, UDS and  $\overline{LDS}$  for control.

- During a byte-read operation, the μP will select the correct half of the data bus depending on whether it's an even or odd address (similar to 8086). (However, most designs provide separate read strobes for even and odd banks.)

- Separate write strobes are required for even and odd banks so that data is not written to the wrong memory bank.

#### Motorola 68000 $\mu$ P – Memory Interfacing

• Block diagram of DTACK circuit:

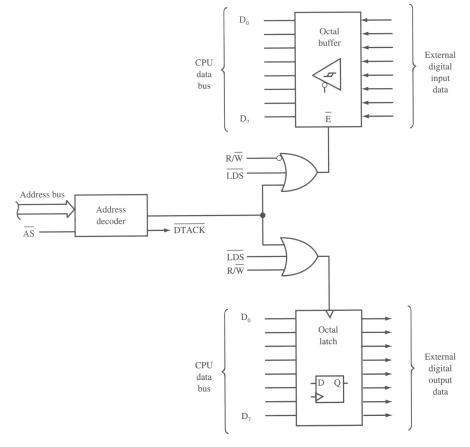

#### Motorola 68000 $\mu$ P – I/O Interfacing

- All I/O is memory-mapped.

- Decoding is the same as for memory.

- One still must generate DTACK.

Would require another buffer/latch pair for UDS for a 16-bit I/O interface. (connected to  $D_{15}$ - $D_8$ ).

FIGURE 9.1 Memory-mapped I/O circuitry

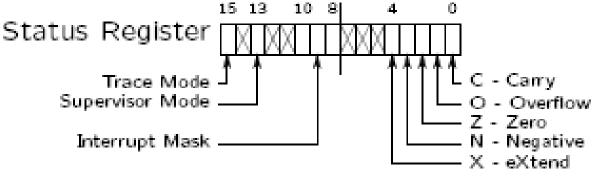

- The 68000 has three execution states:

- 1. Normal running user program.

- 2. Halted not executing instructions. (perhaps because of a system failure such as a double bus fault, or due to HALT pin).

- 3. Exception (processing) state includes interrupts, but goes beyond the usual notion of interrupts.

- Two privilege states.

- User and Supervisor.

- Some instructions are only available in supervisor state.

- STOP, RESET, RTE, MOVE/AND/EOR/OR to SR, MOVE to USP

- Separate stack pointers.

- Provides security for operating systems etc.

- All exception processing is done in supervisor state.

- The only way to get to supervisor state is through an exception (or reset).

- Can use privilege state for memory management

- i.e. include FC2-pin in memory interface.

FIGURE 4.3 User/supervisor memory partitioning

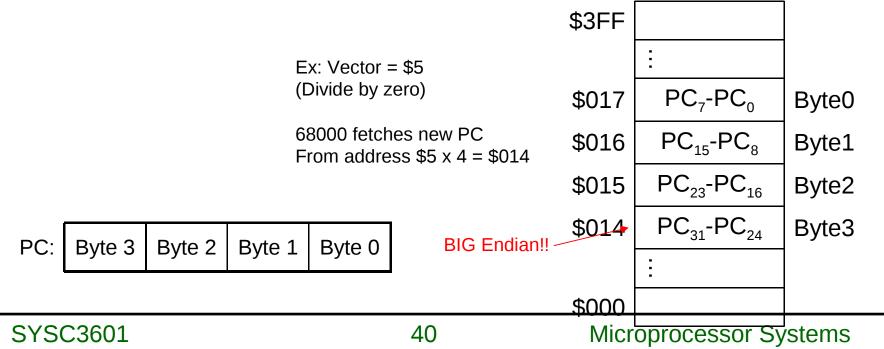

- Interrupt Vectors and the vector table

- A vector number is one byte (0-255)

- Vector Table:

- Occupies the first 1kbyte (000-3FF) of memory.

- Each entry (except the first) is a 32-bit address pointing to the start of the exception handler code.

|                    | Address |            |                    |                                       |

|--------------------|---------|------------|--------------------|---------------------------------------|

| Vector Numbers     | Dec     | Hex        | Space <sup>2</sup> | Assignment                            |

| 0                  | 0       | 000        | SP                 | Reset: Initial SSP <sup>3</sup>       |

|                    | 4       | 004        | SP                 | Reset: Initial PC <sup>3</sup>        |

| 2                  | 8       | 800        | SD                 | Bus error                             |

| 3                  | 12      | 00C        | SD                 | Address error                         |

| 4                  | 16      | 010        | SD                 | Illegal instruction                   |

| 5                  | 20      | 014        | SD                 | Zero divide                           |

| 6                  | 24      | 018        | SD                 | CHK instruction                       |

| 7                  | 28      | 01C        | SD                 | TRAPV instruction                     |

| 8                  | 32      | 020        | SD                 | Privilege violation                   |

| 9                  | 36      | 024        | SD                 | Trace                                 |

| 10                 | 40      | 028        | SD                 | Line 1010 emulator                    |

| 11                 | 44      | 02C        | SD                 | Line 1111 emulator                    |

| 12 <sup>1</sup>    | 48      | 030        | SD                 | (Unassigned, reserved)                |

| 13 <sup>1</sup>    | 52      | 034        | SD                 | (Unassigned, reserved)                |

| 14                 | 56      | 038        | SD                 | Format error <sup>4</sup>             |

| 15                 | 60      | 03C        | SD                 | Uninitialized interrupt vecto         |

| 16–23 <sup>1</sup> | 64      | 040        | SD                 | (Unassigned, reserved)                |

|                    | 92      | 05C        | 02                 |                                       |

| 24                 | 96      | 060        | SD                 | Spurious interrupt <sup>5</sup>       |

| 25                 | 100     | 064        | SD                 | Level 1 interrupt autovector          |

| 26                 | 104     | 068        | SD                 | Level 2 interrupt autovector          |

| 27                 | 108     | 06C        | SD                 | Level 3 interrupt autovector          |

| 28                 | 112     | 070        | SD                 | Level 4 interrupt autovector          |

| 29                 | 116     | 074        | SD                 | Level 5 interrupt autovector          |

| 30                 | 120     | 078        | SD                 | Level 6 interrupt autovector          |

| 31                 | 124     | 07C        | SD                 | Level 7 interrupt autovector          |

| 32-47              | 128     | 080        | SD                 | TRAP instruction vectors <sup>6</sup> |

|                    | 188     | 0BC        | 00                 |                                       |

| 48–63 <sup>1</sup> | 192     | 0C0        | SD                 | (Unassigned, reserved)                |

| 10 00              | 255     | 0CU<br>0FF | 50                 |                                       |

| 64–255             | 256     | 100        | SD                 | User interrupt vectors                |

| JT 200             | 1020    | 3FC        | 30                 | User interrupt vectors                |

<sup>1</sup>Vector numbers 12, 13, 16 through 23, and 49 through 63 are reserved for future enhancements by Motorola. No user peripheral devices should be assigned these numbers.

<sup>2</sup>SP denotes supervisor program space, and SD denotes supervisor data space.

<sup>3</sup>Reset vector (0) requires four words, unlike the other vectors, which only require two words, and is located in the supervisor program space.

<sup>4</sup>MC68010 only. This vector is unassigned, reserved on the MC68000 and MC68008.

<sup>5</sup>The spurious interrupt vector is taken when there is a bus error indication during interrupt processing. <sup>6</sup>TRAP #n uses vector number 32 + n.

• Exception Processing Sequence

1. Save the status register in a temporary register and set the S-bit so that the 68000 can enter supervisor mode.

- 2. Get the vector number. There are several ways:

- (a) may be determined internally by processor.

- (b) external interrupts can be "auto-vectored" (to come).

- (c) external interrupts can provide a vector number (i.e. type) on  $D_7 D_0$  during the interrupt acknowledge cycle.

- 3. Save processor information onto supervisor stack:

- (a) push PC low word.

- (b) push PC high word.

- (c) push status register (from saved temporary unmodified version).

- 4. Fetch new PC from the vector table.

- 5. Execute exception handler.

- 6. Return with RTE. Pops SR, then PC.

- Note: Exceptions can be nested not masked automatically like 8086 does.

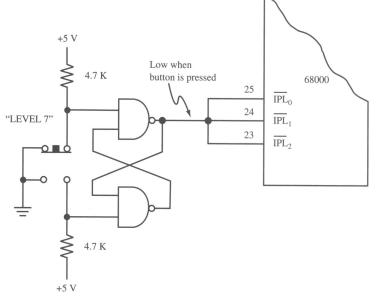

- 68000 Hardware Interrupts

- Seven levels of external interrupts depending on  $\overline{IPL2}$ ,  $\overline{IPL1}$ , and  $\overline{IPL0}$ .

- Level 0, all  $\overline{IPLS} = 1$ , no interrupt.

- Level 7, all  $\overline{IPLS} = 0$ , highest priority (non-maskable).

- Interrupt priority mask (bits 8, 9, and 10 of SR) is set to disable lower priority interrupts.

Example circuit to generate a level-7 interrupt using a single push-button.

We can develop more complex circuits to generate multiple interrupt levels depending on the source of the interrupt request.

FIGURE 7.10 Generating a level-7 interrupt with a pushbutton

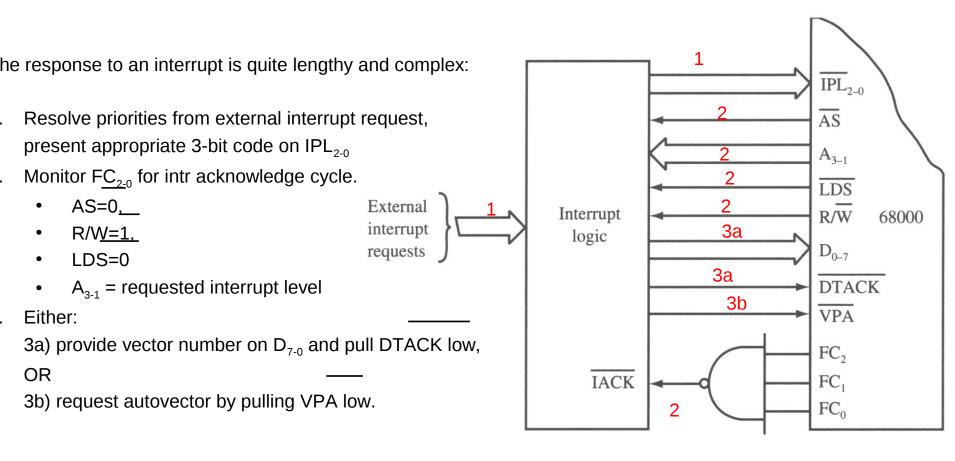

- Interrupt Acknowledge Cycle

- (asynchronous, hardware interrupt requests)

- 1. Device and interrupt logic set IPL2, IPL1and IPL0.

- 2.  $\mu$ P completes current instruction.

- 3.  $\mu$ P enters interrupt acknowledge cycle.

- Interrupt Acknowledge Cycle con't

- 4. External logic may do one of two things:

- (a) Supply a vector number.

- Place 8-bit vector number of  $D_7 D_0$ .

- pull DTACK low.

- $\mu P$  will read  $D_7 D_0$ .

- (b) Request an "auto-vector".

- Pull VPA low. Leave DTACK high.

- $\mu P$  generates its own vector based on interrupt level first supplied to IPL inputs.

- autovectors point to locations \$064 through \$07F in vector table.

- Autovectors should be used whenever 7 or less interrupt types are needed.

- 5. Proceed with exception handling steps from slide 42

FIGURE 4.9 External interrupt circuitry block diagram

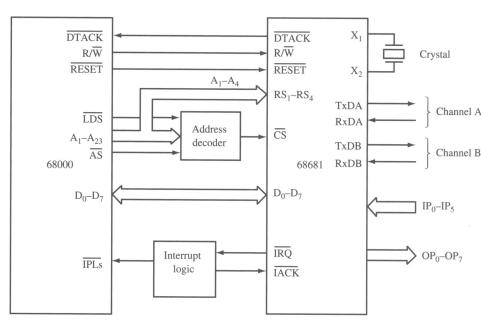

### 68681 DUART

- Contains 2 UARTs, independently programmable

- Both channels can provide simultaneous Tx/Rx.

- Interface using internal control/data/status registers selected via RS<sub>4-1</sub> pins.

- Also provides 6 parallel inputs and 8 parallel outputs

- Can be used for handshaking signals or standard I/O pins.

FIGURE 10.17 Using the 68681 in a 68000-based system

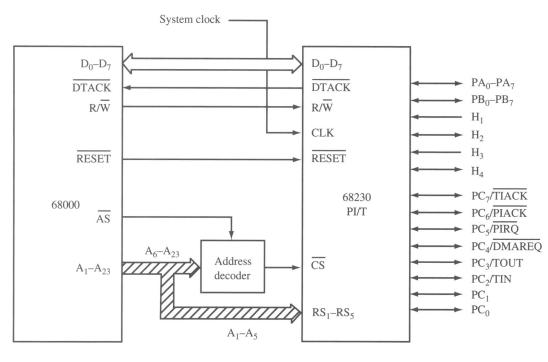

### 68230 Parallel Interface/Timer (PI/T)

- Contains 3 8-bit parallel ports

- Can be input, output, bidirectional

- Ports A&B can form 16-bit port

- Also contains an internal 24 bit timer

- Count down, square wave generator, etc.

- 23 internal data/control/status registers selected via RS<sub>5-1</sub> pins.

- H<sub>4-1</sub> pins are handshaking for ports A&B

- Can cause interrupts

- PortC can be used as general I/O pins, interrupt request/acknowlege, timer inputs/outputs, or DMA request.

Note:  $PC_2$ - $PC_7$  are dual function pins.

FIGURE 10.25 Interfacing the 68230 PI/T

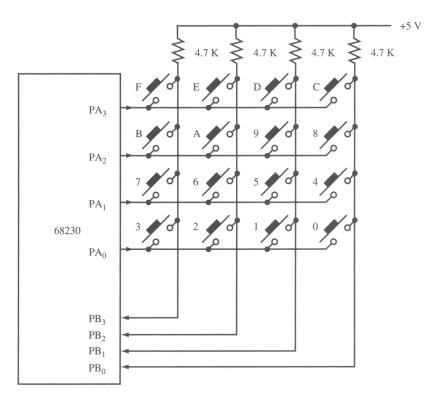

#### Keyboard scanning with a 68230 PI/T

- Drive PA<sub>3-0</sub> in sequence

- Read PB<sub>3-0</sub> to check for key depressed

FIGURE 10.32 Sixteen-key keypad scanner using the 68230

| <b>TABLE 10.1</b> | Keyboard |  |  |  |  |

|-------------------|----------|--|--|--|--|

| scanning codes    |          |  |  |  |  |

| F      | Parallel        | outputs         |                 |                 |

|--------|-----------------|-----------------|-----------------|-----------------|

| $PA_3$ | PA <sub>2</sub> | PA <sub>1</sub> | PA <sub>0</sub> | Buttons scanned |

| 1      | 1               | 1               | 0               | 3, 2, 1, 0      |

| 1      | 1               | 0               | 1               | 7, 6, 5, 4      |

| 1      | 0               | 1               | 1               | B, A, 9, 8      |

| 0      | 1               | 1               | 1               | F, E, D, C      |

### Microprocessor Systems

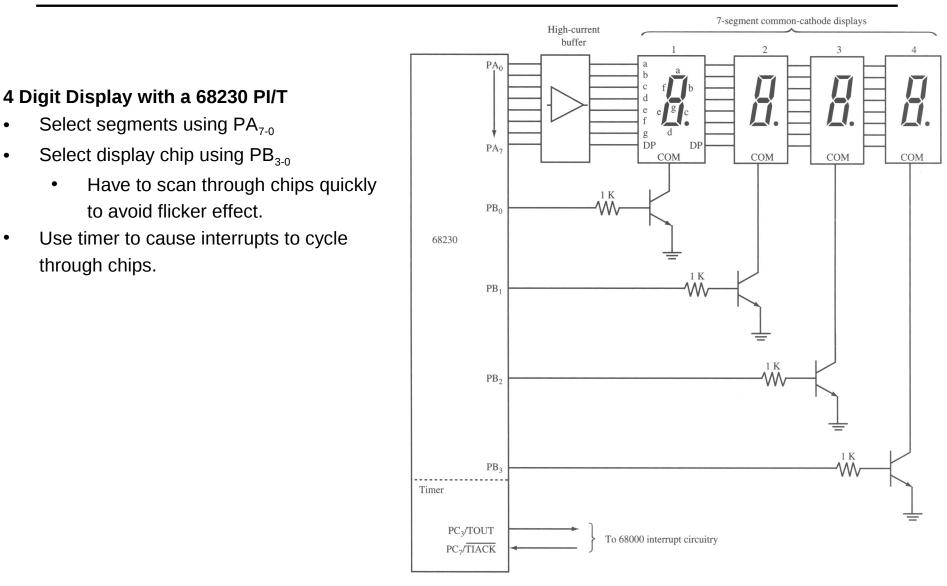

FIGURE 10.33 A four-digit multiplexed display

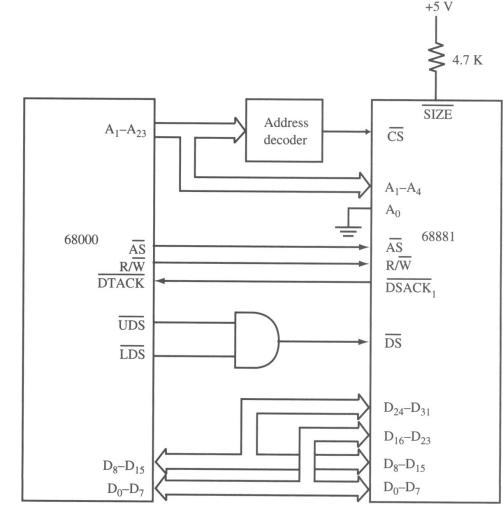

#### 68881 Math co-processor

- Similar to 8087

- 8 Internal 80-bit floating point registers

- 40 floating point instructions

- 32-bit data bus

- Optimally used with 68020 (32-bit bus)

- $A_0$  and SIZE are used to configure the 68881 for the size of the  $\mu$ P's data bus.

FIGURE 10.39 Floating-point coprocessor connections to the 68000

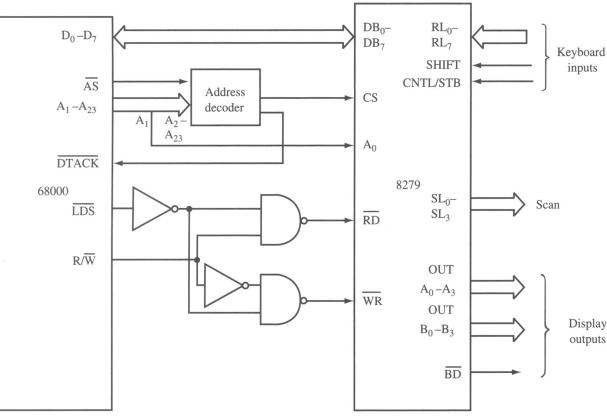

### INTEL 8279 Keyboard/Display Chip

- For non-68000 series chips, must generate DTACK signal using interface circuitry.

- Must also create separate RD and WR signals from joint R/W

#### Other peripheral chips:

68153 BUS Interrupt Module 68440 Dual DMA Controller 6851 Memory Management Unit 68901 Multifunction Peripheral 68465 Floppy Disk Controller 68452 Bus Arbitration Module 68590 LAN Controller for Ethernet 68652 Multiprotocol Communications Controller 68824 Token-Passing Bus Controller 68486/68487 Raster Memory System 68184 Broadband Interface Controller

FIGURE 10.41 Interfacing the 8279 to the 68000

SYSC3601